DoD had been using mp systems since the late 1960s...

Absolutely true.

Quoting a subsequently Declassified, Top Secret

1972 report about Safeguard Development Status -

Code:

IV. Technical Progress

The research and development portion of the Safeguard

program is progressing satisfactorily. The prototype Missile Site

Radar (MSR) located at the Kwajalein Missle Range began radiating

power in September 1968 and has been operating since that time. It

has met or bettered all of it's design objectives and no serious

deficiencies have been found. Beginning in March 1969, check-out

of the MSR data processing system was initiated and successful opera-

tion of four data processing units working in parallel has since been

achieved. MSR software for the first part of the system test program

has been completed and installed. Beginning in July of 1969, tracking

of local targets was accomplished with the initial software and, in

December 1969, two ICBMs launched from Vandenberg AFB, California,

were successfully tracked.

A final stage Multiprocessor system was demonstrated at Bell Labs Whippany, in April 1969. I know this to be true, because the software development for Safeguard was done in my home town.

Furthermore, Safeguard was an outgrowth of previous ABM programs. Bell Labs was involved as early as 1955 on studies and concepts that would lead to systems phases like NIKE-ZEUS, NIKE-X, SPARTAN which used less sophisticated processor concepts as far back as 1962 culminating in the first successful ICBM intercept in July of that year. The phrase "

Hitting a bullet with a bullet" is used in the report. Based on that experience, Bell Labs realized a multiprocessor approach was required.

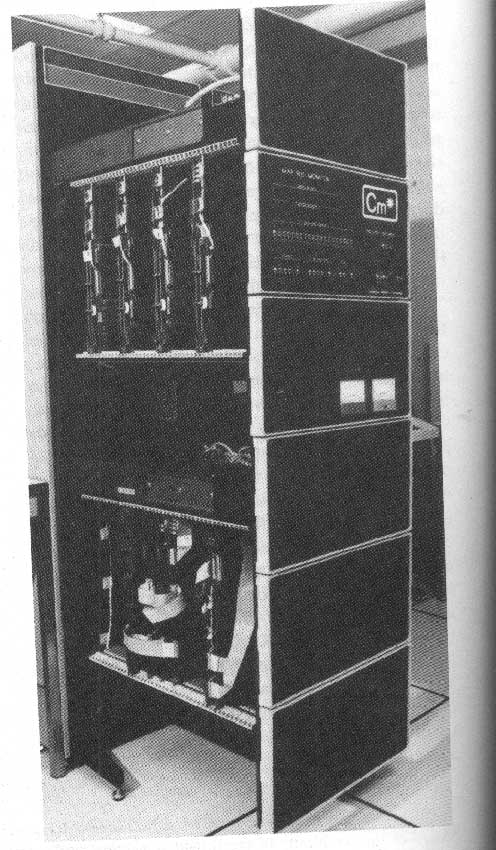

The uniqueness of SAFEGUARD is that in 1963, Bell Labs in cooperation with UNIVAC, undertook the task of creating such a data processing system using

integrated circuits specially manufactured by Western Electric [ultimately named as Prime contractor] in direct opposition to expert opinion of the American Academy of Sciences who claimed such a system could not meet the required calculations per second (30 MIPS) or reliability needs, predicted by Bell Labs.

The proof of concept system, called

PEPE (Parallel Element Processing Ensemble) - was built on an IBM 360/65 as a host computer "in the mid 60's". This "IC model" showed the feasibility of the Multiprocessing approach, Validating the use of more advanced

large scale integrated circuits to be used in the final version.

Ultimately, the Safeguard System would exceed all requirements and become the world's first successful,

Operational computer directed "Phased Array Radar" ABM system.