I had a stupid idea and I want to share it, sorry for that.

What I liked in 6502 (like in LSI-11) was the variety of address modes.

This post may carry highly erroneous statements, I go back to the 65xx family after nearly 40 years of errance on unrelated topics.

On NMOS 6502 there are a number (14?) of 16 bits addressing modes.

- Absolute

- Absolute Indexed with X

- Absolute Indexed with Y

- Absolute Indirect JMP

On 65c02 there is in addition:

- Absolute Indexed Indirect

The 65c816 adds 24 bits addressing modes including:

- Absolute Long

- Absolute Long Indexed with X (X may be 16bits)

- Absolute Indirect Long

So for symmetry's sake the 65c816 is missing:

- Absolute Long Indexed with Y (X may be 16bits)

=> 1. What if a bit mode would enable this Absolute Long Indexed with Y ?

If we look at page zero addressing we can make a similar observation:

The 65c816 adds Zero page addressing modes in first 64K addresses.

=> 2. What if a bit mode would enable Zero page addressing modes in 16M addresses?

=> 3. What if a bit mode would enable Direct Page Indexed long Indirect with X (Preindexed)

On NMOS 6502:

- Zero Page

- Zero Page Indexed with X

- Zero Page Indexed with Y

- Zero Page Indirect Indexed with Y (Postindexed)

- Zero Page Indexed Indirect with X (Preindexed)

On 65c02 there is in addition:

- Zero Page Indirect

The 65c816 adds these addressing modes:

- Direct Page Indirect Long

- Direct Page Indirect Long Indexed with Y

So for symmetry's sake the 65c816 is missing:

- Direct Page Indexed long Indirect with X (Preindexed)

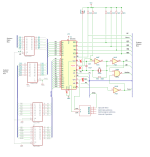

* I think the point 1. is feasible with a simple proposal similar in principle to LAUGHTON ELECTRONICS' KimKlone

When a mode bit would enable it, the "Absolute Indexed with Y" becomes "Absolute Long Indexed with Y"

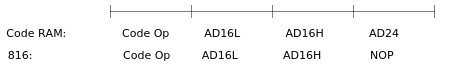

In memory there is:

- Operation code

- AD0-AD7

- AD8-AD15

- AD16-AD24

The 65c816 would "see"

- Operation code

- AD0-AD7

- AD8-AD15

- NOP

An external circuitry would:

- decode the Fetch cycle (with VPA/VPB)

- store AD16-AD24 in a buffer

- When the read or write cycle would happen, the AD16-AD24 value from this buffer would be used as AD16-AD24.

* I think the point 2. (enable Zero page addressing modes in 16M addresses) is feasible with this proposal:

- decode the Fetch cycle (with VPA/VPB)

- When the read or write cycle would happen, the AD16-AD24 value comes from a 8 bits buffer and would be used as AD16-AD24. There could be multiple (many) such buffers.

- Alternatively, When the read or write cycle would happen, the AD8-AD24 value comes from a 16 bits buffer and would be used as AD8-AD24.

* I think the point 3. (Direct Page Indexed long Indirect with X) is feasible with this proposal:

- decode the Fetch cycle (with VPA/VPB)

- When the read or write cycle would happen, the AD16-AD24 value from a buffer would be used as AD8-AD24. There could be multiple (many) such buffers.

Is this absolutely useless or are some bits may be valuable?

Jean-Pierre