So I have simulated the schematic and found something interesting...

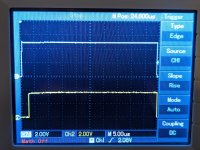

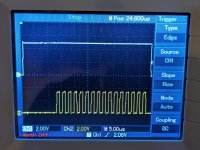

With D5=0 I get 17 pulses and with D5=1 I get 33 pulses (but the first intermediate pulse is missing).

For some reason my IC8/6 pulses are inverted when compared with your oscilloscope traces... Ah I have coded a NAND gate instead of an AND gate - so I can't get too excited about that!

I am beginning to suspect that the test procedure is incorrect...

If the image is in 512B of memory (D5=0) then there are 16 bytes per line.

If the image is in 2KB of memory (D5=1) then there are 32 bytes per line.

Not sure why there is an extra pulse (16 vs 17 and 32 vs 33) but I suspect either the first (or last) pulse perform a unique function other than (or as well as) performing a DMA.

I am now really convinced that the Cromemco manual is wrong.

Dave

In other TTL logic systems I have analysed, ones which ultimately generate video, timing is everything. When pulses are divided down from a master clock, it helps to use synchronous counters, still later, with whatever pulses are derived they can have an awkward relationship to the rising or falling edge of the clock, elsewhere after the delays of other gates are accounted for, making them dependent on the particular device properties. It is interesting though that they delayed the inputs to IC8 on pins 5 & 4. It might be that there is supposed to be an extra pulse in the train, and it simply gets ignored later due to timing considerations. Or maybe the simulated circuit simply behaves differently. I would have to get my Dazzler running and check with the scope.

I guess the manual could be wrong...... If it was it would have meant, at the time, not many people would have been able to get their Dazzlers working and they would have ended up at Cromemco's repair Dept. You would think they would have picked up on the reason why and sent out an errata sheet.

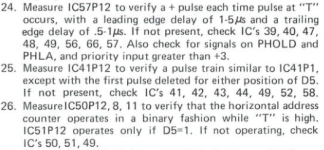

Looking at the scope recording on post #547 there are 17 pulses there. I agree, one pulse presumably the leading wider one they talk of has another application, so it is out by a factor of 2 with respect to the 16 pulses, that should be 32, something must have gone awry with the gating of the signals from the 74161 counters or possibly the pre-load values of the counters from pin 6 of IC21. That is if we believe the manual. But your simulation agrees with what

@nullvalue is seeing, making the manual look very suspicious. But, they seem very definite about what pulses should be there.

When I can clear the bench I'll fire up my Dazzler and check.