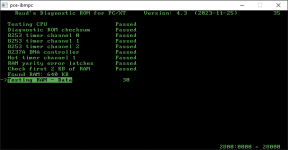

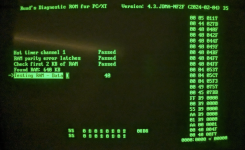

TEST5060 & TEST5067 Look good so RAM should be good to go, however RDR now consistently fails all the 8253 timer channels. Even though the 8253 is a solid IC, I had myself convinced it could be faulty. Socketed and swapped out with known good, timers still fail so ruled that out.

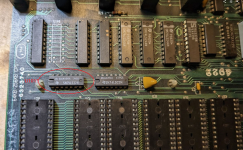

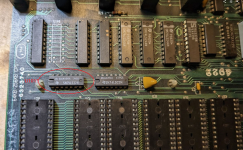

I started poking around some more, and found out /XIOW isn't active during the timer tests, it just stays high. At first I was baffled because the schematics say /XIOW & /XIOR go back to U14, but there wasn't any connectivity on the board. So I took a look at the traces, and on these 64-256 type boards they go back to U101:

/XIOR U34-22 -> U101-6

/XIOW U34-23 -> U101-3 (ISSUE HERE)

U101 Doesn't even seem to be documented anywhere, or did I miss it? So I guess I'll be having a look at that IC.

I started poking around some more, and found out /XIOW isn't active during the timer tests, it just stays high. At first I was baffled because the schematics say /XIOW & /XIOR go back to U14, but there wasn't any connectivity on the board. So I took a look at the traces, and on these 64-256 type boards they go back to U101:

/XIOR U34-22 -> U101-6

/XIOW U34-23 -> U101-3 (ISSUE HERE)

U101 Doesn't even seem to be documented anywhere, or did I miss it? So I guess I'll be having a look at that IC.