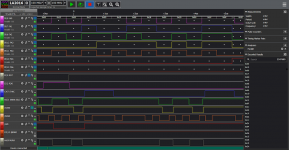

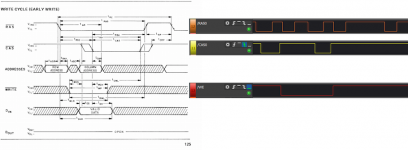

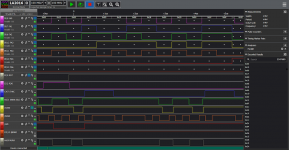

I finally got a little quality time with the PET tonight. I took some traces with the walking bit test. Here is an example of it when it is writing a "1" to RD7 at address $00 and reading it back.

To my eye, this looks correct.

I've also played around with the machine quite a bit. It boots to basic, I can type in programs and the run, etc. I haven't tried loading things from cassette as my datasette needs to be serviced. I have successfully loaded things from "disk" (PET2SD) repeatedly with success and played a few games, etc., that all seem to play and run normally (although sometimes the keybindings are weird, presumably because I have a business keyboard and the games don't take that into account.) No random drops into the ML monitor or anything. It currently seems to be 100%.

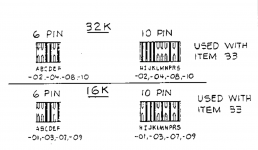

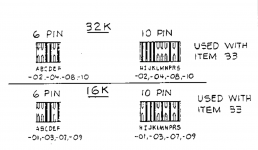

I also installed 8 new sockets to upgrade the RAM to 32k. However, I haven't been able to get the second bank of RAM to be recognized correctly, at least by BASIC. I think this is probably because of the jumper settings. Here is a photo of the two jumper blocks as they are now, working properly with 16k of RAM:

Pretty nasty and rusty looking, I know, but has good continuity across all the unbroken links. BTW, this is how basically every IC on the board looked when I started working on it. I haven't touched these since I thought the type of jumper was interesting and knew I can't replace them. By eye and by my meter, this is how they're configured:

A: open

B: open

C: shorted

D: open

E: open

F: shorted

H: shorted

I: shorted

J: shorted

K: open

L: open

M: open

N: open

P: shorted

R: open

S: shorted

If we compare refer to the documentation at

http://www.zimmers.net/anonftp/pub/cbm/schematics/computers/pet/2001N/320351-6.gif, the jumpers when used with 4116 RAM (the mentioned item 33) should be set like this:

Neither the 16k nor the 32k configuration correspond to what I have on my board, working with 16k.

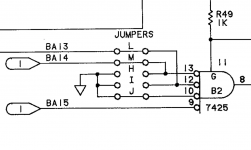

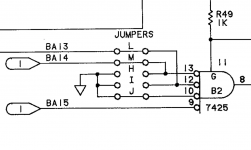

If we refer to jumper block in the RAM schematic at

http://www.zimmers.net/anonftp/pub/cbm/schematics/computers/pet/2001N/320349-5.gif

This looks to me like maybe L and M should be open and H, I, and J should be shorted, which is how the board is set (for 16k) and what is indicated in the document for 32k. Other jumpers in the schematic and on my board (A, B, C, E, F) agree with the document. I can't find any of the other jumpers in the schematic (D, K, N, P, R, S), so no idea about those.

So, does any one know what the correct jumper settings for 16k or 32k are?

If I need to short any of these, does any one know if that's possible using these same blocks? Should I replace them with pin headers and regular jumper caps? Should I keep the jumpers as they are and if I need to short them should I just solder a bodge wire to the bottom of the board to keep these looking original?

Or, does it seem like it's not a jumper problem and I should start beeping out traces and looking at signals on the second bank of RAM?

Cheers,

Greg

>>> I know Dave doesn't like swapping stuff randomly, but

It worked, so I would take it!

Good to see that it passes my PETTESTER code (that is a pretty stressful test). However, I would still try our walking ‘1’ test just to make sure that doesn’t identify something awry.

Since you now have a socket in there for the 74x74 (H1) I would take s logic analyser trace (with the walking ‘1’ test that you have previously validated still works) to check what has happened to ‘fix’ the timing.

The worst case scenario here is that you are masking the problem by changing H1 rather than fixing the problem. If it was borderline erroring before, it may be borderline working now?

I will take a look at the schematics on Monday. I have another project to do today (housework)...

If you are going to keep the PET for your own purposes then I would upgrade to 32K (to run larger programs). But use IC sockets of course just in case the upgrade causes problems... But’s that only my opinion of course...

Dave