Ttpilot

Experienced Member

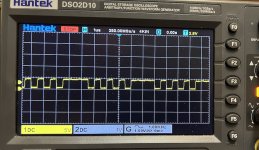

My North Star motherboard seems to be in working order (thanks, everyone). I decided to plug in my Compupro CPU-Z board and try to sort it out. At first it seemed to be working okay, at least I was getting a good clock signal and RESET* seems to work. I installed a couple of 2kx8 EPROMS that consist of NOPs with a jump back to 0000h at the end. I attached a logic analyzer to the address pins of the Z80 and got this

It's obviously not progressing through the addresses or reading the EPROM. The other signals look wacky, too

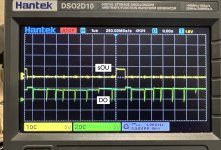

Here's the clock M1* (pin 27) and CLK (pin 6). These don't look right. I've got another Z80 coming in I can try. I'm also working on a breadboard setup to test the Z80s

It's obviously not progressing through the addresses or reading the EPROM. The other signals look wacky, too

Here's the clock M1* (pin 27) and CLK (pin 6). These don't look right. I've got another Z80 coming in I can try. I'm also working on a breadboard setup to test the Z80s