m_thompson

Veteran Member

We are getting closer to the cause of the clock data-break problem. When a data-break from the clock is granted, a bit in the microcode gates the Word Count address from the I/O controller to the O bus in the processor. This part is working reliably. There is complex circuitry combined with microcode bits that then gates the Word Count address from the O bus into the Memory Buffer register. This sometimes works OK, sometimes it doesn't. That would make the data-break increment the wrong Word Count address in memory, and cause the clock to work erratically.

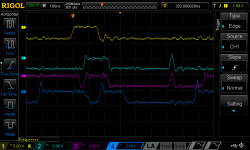

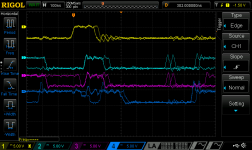

In the first 'scope image below trace 1 is the EXT(1) microcode bit that gates the data-break address onto the O bus. Trace 2 is one of the data-break address bits on the O bus. Trace 3 is the corresponding bit in the MB register. Trace 4 is the MBI(1) microcode bit that actually gets set by complex circuitry. When trace 4 goes low coincident with trace 2, the data bit gets latched into the MB.

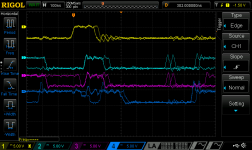

As shown below sometimes the MB(1) bit doesn't get set, and the data-break address doesn't get latched into the MB. Since this is a very asynchronous machine, there are 6 B310 adjustable delay lines in some really complex Control Memory timing circuitry that eventually should set the MB(1) bit. If the cumulative delay is off by 25 ns or so, the AND gating logic doesn't work and MB(1) won't get set. You will also artifacts where signals get enabled for a short time when they shouldn't. That is probably what is making the spikes on traces 2 & 3.

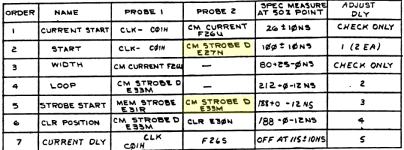

What we need to do now is check the Control Memory timing adjustments, and look for jitter on any of the clock signals. There are wire-wrap jumpers on the processor backplane that can be changed to adjust the timing of each delay.

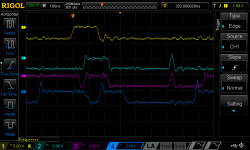

I think that we have something in the clock circuitry that is intermittent and is causing jitter in the clock signals. We have had this problem before with the B310 flipchips shown below. The long black devices are inductive delay lines. They have 5 wires on the back soldered to the PCB. Because of the difference in thermal expansion between the delay line and the PCB the solder joints crack and go intermittent. The newer versions of the N310 have the delay lines rotated 90 degrees to the PCB so there is some wire between the delay line and the PCB that can flex and absorb the thermal expansion. We don't have enough of the newer B310 modules to replace them all. We could also have a failing transistor on one of the delay lines, or elsewhere in the CM timing circuitry that is causing the jitter.

In the first 'scope image below trace 1 is the EXT(1) microcode bit that gates the data-break address onto the O bus. Trace 2 is one of the data-break address bits on the O bus. Trace 3 is the corresponding bit in the MB register. Trace 4 is the MBI(1) microcode bit that actually gets set by complex circuitry. When trace 4 goes low coincident with trace 2, the data bit gets latched into the MB.

As shown below sometimes the MB(1) bit doesn't get set, and the data-break address doesn't get latched into the MB. Since this is a very asynchronous machine, there are 6 B310 adjustable delay lines in some really complex Control Memory timing circuitry that eventually should set the MB(1) bit. If the cumulative delay is off by 25 ns or so, the AND gating logic doesn't work and MB(1) won't get set. You will also artifacts where signals get enabled for a short time when they shouldn't. That is probably what is making the spikes on traces 2 & 3.

What we need to do now is check the Control Memory timing adjustments, and look for jitter on any of the clock signals. There are wire-wrap jumpers on the processor backplane that can be changed to adjust the timing of each delay.

I think that we have something in the clock circuitry that is intermittent and is causing jitter in the clock signals. We have had this problem before with the B310 flipchips shown below. The long black devices are inductive delay lines. They have 5 wires on the back soldered to the PCB. Because of the difference in thermal expansion between the delay line and the PCB the solder joints crack and go intermittent. The newer versions of the N310 have the delay lines rotated 90 degrees to the PCB so there is some wire between the delay line and the PCB that can flex and absorb the thermal expansion. We don't have enough of the newer B310 modules to replace them all. We could also have a failing transistor on one of the delay lines, or elsewhere in the CM timing circuitry that is causing the jitter.