Hi

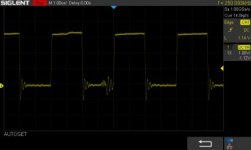

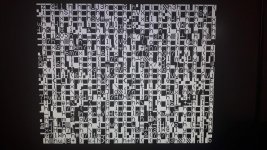

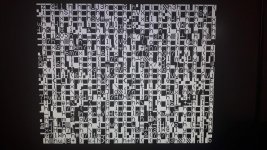

My pet 3032 has the problem of garbage screen

I have checked all pcb voltages and they are correct. + 5V, + 12V, -5V and + 9V, according to the diagrams:

http://www.zimmers.net/anonftp/pub/cbm/schematics/computers/pet/2001N/320349-1.gif

to

http://www.zimmers.net/anonftp/pub/cbm/schematics/computers/pet/2001N/320349-8.gif

I have checked the ram and roms with the http://blog.tynemouthsoftware.co.uk/2015/09/commodore-pet-rom-ram-replacement-boards.html and they are ok.

When boot with replacement boards the same

The difference is that if I press the reset button on the replacement board it loads the basic screen but with garbage, whether I use the board roms/rams or replaced roms/rams

Help me please

My pet 3032 has the problem of garbage screen

I have checked all pcb voltages and they are correct. + 5V, + 12V, -5V and + 9V, according to the diagrams:

http://www.zimmers.net/anonftp/pub/cbm/schematics/computers/pet/2001N/320349-1.gif

to

http://www.zimmers.net/anonftp/pub/cbm/schematics/computers/pet/2001N/320349-8.gif

I have checked the ram and roms with the http://blog.tynemouthsoftware.co.uk/2015/09/commodore-pet-rom-ram-replacement-boards.html and they are ok.

When boot with replacement boards the same

The difference is that if I press the reset button on the replacement board it loads the basic screen but with garbage, whether I use the board roms/rams or replaced roms/rams

Help me please