Tronix

Experienced Member

Also what is that red motherboard in your photo? it looks awesome

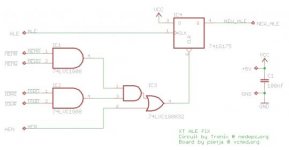

This is new replica of the old Soviet computer named Poisk-2. Full length AT mainboard based on KM1810VM86M (8086) CPU with some usable things, such us 2 Mb onboard RAM (640Kb base memory and ~1400Kb for EMS), onboard RTC. BIOS contain "Set-Up" program like "Set-Up" in AT class machines for configure Time, Date, FDD, HDD and other settings. Also for some reasons BIOS contain build-in memory remapping procedures. When one of the DRAM chips is out of order, BIOS correct buildin "DRAM deffect map" and shift up logical memory space up. Thus, computer still usable. KM1810VM86M processor is not 100% clone Intel 8086. He contain some 80186 instruction (pusha, popa) and one very important thing - when invalid opcode occured he generate exception. Therefore, there are 80286 processor emulators exist.

There is description with photos about replica creation: https://geektimes.ru/post/294155/ (in Russian languarge). Project now open-source. Gerber, circuit and other files here: https://github.com/Haper/poisk-2-mainboard .