PALs are not reprogrammable. They're like PROMs, IE, they have literal tungsten fuses in them and once they're blown they're blown.

Hi Eudimorphodon,

Thanks for your elaborate explanation, I appreciate the effort you made and the time you took to help me by pointing to some important aspects involved since this is new to me. This saves me a lot of time to read these things from you since you already have experience, so thanks for the friendly help! If you have any other things you want to share, it's welcome to share it here if you have time.

I made the error indeed to assume that I can erase PAL chips. So another thing learned now.

Which explains the type differences and those types I could not find in the programmable type list in my device.

Yesterday I jumped into the rabbithole of programmable logic, but I am used to that because my whole PC projects are all big rabbit holes where you have to jump in and stay in. I spent some time searching methods and finally settled on using WinCupl which still works in Windows 10. Or else I have some older PCs available to use if needed. It is indeed cranky as you say but I don't mind that, at least it can provide a solution that works and it is GUI-based.

I experimented a little with the syntax in WinCupl by first only defining the pins and compiling an "empty" chip, where I picked G16V8A in the "device" field.

Compiling an empty chip was finally successful so I proceeded to write some simple equations, first one, then another.

Each time I did a compile action until there were no errors in the syntax.

I assume the syntax of equations in WinCupl is much like doing calculations where you first do the multiplications, then the sums etc. So AND goes before OR. However I was not sure so I used brackets to include circuits in the formula just to be sure.

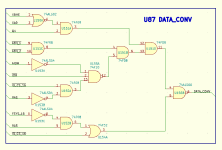

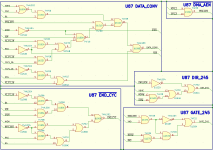

By the time I defined DATA_CONV it did get a little complicated so I finally started to use colours for the different areas to keep an overview. I was already sure I was over complicating it for myself but I continued until I at least got the whole equation defined in one line. Next time I get this kind of situation I will redraw the schematic in the form of AND terms which I can then get a better overview and I could try it without brackets later. Compiling my bracket version went fine so I proceeded to generate a .jed "fuse map" file which needs a few options to be enabled in WinCupl as I found out. After getting the .jed file it was the next step to proceed with the programmer.

I use an old Galep-III programmer which lists a number of known devices from manufacturer categories including some PAL types. Possibly certain special newer PAL type chips are erasable, I suspect this because the device lists these to be able to be erased. ICs you can erase are always bold letters in the list and allow to be selected as a "to be programmed" device. Though lets forget it since I don't have any those bold type ICs which would more closely match the PAL16L8 used in that time period. I would prefer some slower device to better match with what IBM did in the 5170, but I am willing to experiment. I do prefer devices which are more programmer friendly if possible, like the GAL.

After trying to erase some PAL chips which failed because they were OTP chips, I moved on to some GAL chips which I found later on some obsolete PCBs. I tried a Lattice GAL16V8A which programmed fine and was listed exactly with that type in the software. Ok, progress!

After programming the chip I plugged it into my test board which lit up some outputs with LEDs which looked promising.

I toggled a few buttons on the inputs which resulted in some familiar responses from the GAL.

After which I built up my 5170 mainboard on my table and plugged in the programmed GAL.

Unfortunately, which I expected would be a possibility but let's try anyway, no POST and no image on the VGA and no beeps either.

So on the hardware level the 5170 is not getting through to any level of being able to function yet with the equations I have assembed so far. So it's back to evaluate everything further, but it is still a level of progress now because I have a path to the GAL device from a situation of using equations. Indeed, if one GAL can replace more than 10 normal ICs that does have possibilities in certain large volume TTL logic systems.

Thanks a lot for the explanations, I will look at the IBM PAL again in the circuit.

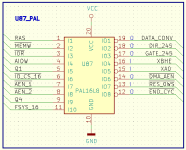

As the IBM schematic lists a "HAL16L8" which I think is a kind of factory produced PAL with fixed contents, I think the "L8" denotes that it is not a registered chip, so it doesn't contain latches, I am thinking the same thing, that it's probably a simple type of PAL programming here in the 5170, though it may still be a little more complex than I hoped.

I checked a PAL datasheet and found some type distinctions.

Where the PAL16L8 is not registered but it does possibly feature an /OE function. I see in the datasheet:

- 10 inputs

- 2 tri-state outputs

(0 registered Q outputs)

- 6 I/O pins

Pin 1-9 and 11 are inputs.

Pin 12 and 19 are the tri state outputs.

Pin 13-18 are the I/O pins.

This is important because the connections in the 5170 circuits to certain pins may provide important clues if those special functions are used.

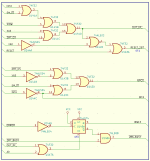

I attached a pin diagram of the connections to U87 here as example.

As we can see where I noted in the diagram at certain pins in the blue text, certain I/O pins were defined as inputs by IBM.

I am not sure if this needs to be specifically listed in WinCupl?

Maybe it does and that's a potential cause of my problem that the 5170 cannot function with the GAL? Though I didn't get any compile errors. I need to learn a few more additional details possibly if this is the case.

I see in the datasheet that there are certain points in the fuse map of the "PAL"L8 types which provide possible connections to each output to provide an /OE function for each pin, if it is optionally programmed to use a /OE function for the pin.

So theoretically any input or other point in the logic equations can provide an /OE function on any of the outputs.

So a certain input or logic statement could provide this. I must say, I have not observed any tri-state behaviour but I don't think that this can be actually observed in my test PCBs. My outputs use a simple 74LS04 inverter to provide LED indication. I should probe the voltage of the outputs without the 74LS04 plugged in so they are not influenced by the LS logic inputs of the 74LS04. Possibly this /OE aspect may complicate things for me now so I should check this on the 5 outputs.

I may have documented the behaviour of the PAL not knowing whether some result is caused by a tri-state situation or not.

I need to look at the connection in the 5170 to see if tri-state could be used anywhere on those outputs in the circuit. I think they are all straight inputs to be driven by single source outputs in those nets.

I will also probe the programmed GAL chip in full detail with the same diagrams I used for assembling the schematic I posted earlier to compare if the GAL behaves 100% identical after programming to what I have observed in the IBM chip so far.