One thing that can sabotage quick fault finding is that there can be two or more problems affecting the computer at the same time. Which can sometimes confound the testing and slow things down.

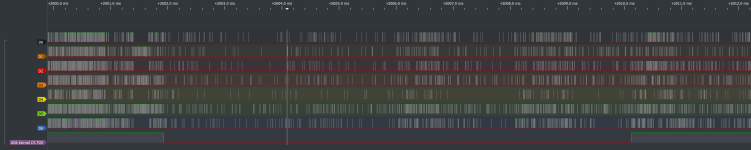

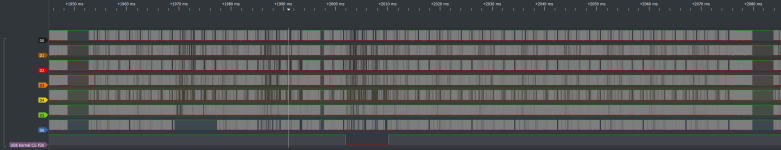

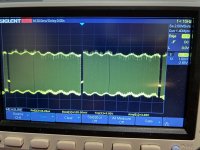

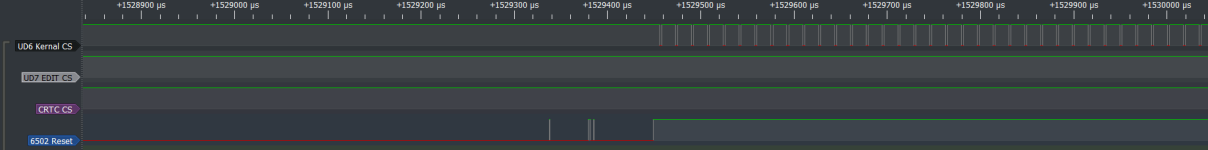

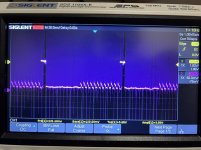

In my PET repair box I made a NOP generator with an on board address range decoder. This way I could use that to sync the scope over a specific address range on one channel, and use the other scope channel to inspect events that were occurring over that range only. I had noticed though using the NOP, on the scope at times there did appear to be some data line conflicts at times, not seen with the computer in normal use.

I also made a circuit where the DRAM is dynamically deactivated below the 1k or 2k boundary and replaced with SRAM switched in (the board on the right in the photo). This way I would recover the operating system if DRAM was damaged and then I could use simple test programs to analyze the DRAM and home in on the defective chips that in many cases are soldered in.

But of all the test circuits I made and Daver2's wonderful PET tester too, the thing I found helpful was to do two things to help speed up a repair.

1) One was to make a full set of good ROM's.

2) Then check all of the ROM's socket pins for tension, using a defunct IC pin soldered to a wire handle, just to make sure all of the ROM IC socket claws were ok.

Then I would simply fit all of the known good ROMs together. This eliminated all of the ROMs & sockets as a cause of the fault, then I could simply get on and find out which other IC's were defective.

If a fault cleared or altered after doing this I would simply then substitute the original ROMs back in, one by one, to find out which ROM/or ROMs were defective. On one PET board I fixed, 3 ROMs were defective !

I'm not sure how they got like that. I assume they were probably plugged in, in reverse, by a previous owner would be my best guess.