daver2

10k Member

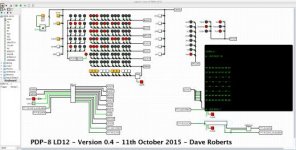

I have just got my TTY hooked up in LOGISIM - the simulation now runs MAINDEC-8I-D02B as well now.

The sample programs for the LD12 TTY do not appear to work. The "Echo program" has a line missing from the bottom of it (i.e. add 0007 5000 JMP 0) and I don't believe that the "Print all possible characters" program works at all.

I will do a bit more testing this week with the MAINDEC-8I diagnostics to see if anything else is revealed before publishing the next version. I have managed to start playing Chess (CHEKMO-II) - but for some reason it is taking a very long time to make its move. This could be due to a 'bug' in my LD12 logic (more testing and checking required on my part) or it is just too slow to run in the LOGISIM environment (I need to make a hardware implementation like Marty!).

I can, however, confirm that signal A0 is *** NOT *** required to be wired up to gate E4/A37 pin 4 in the production of PC(L). This causes the PC to be incremented as part of the interrupt handling process with the result that the return address that is stored is one more than it should be. D02B identified this 'undesirable feature'. Interestingly, it is identical to the bug I had when I did the LD30 microcoded unit...

Dave

The sample programs for the LD12 TTY do not appear to work. The "Echo program" has a line missing from the bottom of it (i.e. add 0007 5000 JMP 0) and I don't believe that the "Print all possible characters" program works at all.

I will do a bit more testing this week with the MAINDEC-8I diagnostics to see if anything else is revealed before publishing the next version. I have managed to start playing Chess (CHEKMO-II) - but for some reason it is taking a very long time to make its move. This could be due to a 'bug' in my LD12 logic (more testing and checking required on my part) or it is just too slow to run in the LOGISIM environment (I need to make a hardware implementation like Marty!).

I can, however, confirm that signal A0 is *** NOT *** required to be wired up to gate E4/A37 pin 4 in the production of PC(L). This causes the PC to be incremented as part of the interrupt handling process with the result that the return address that is stored is one more than it should be. D02B identified this 'undesirable feature'. Interestingly, it is identical to the bug I had when I did the LD30 microcoded unit...

Dave