daver2

10k Member

Looking good so far.

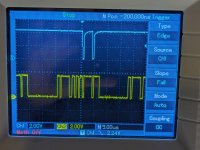

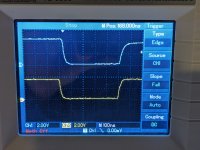

I am guessing the 1 and 2 on the left-hand side indicate the zero reference for channel 1 and channel 2 respectively.

I am also guessing that the blue arrow on the right-hand side is the trigger level. At the moment it is at the bottom. It needs to be halfway between the top and bottom of the indicated signal.

I also notice that the coupling is AC. This needs to be DC for both channels!

See if you can make those changes.

Dave

I am guessing the 1 and 2 on the left-hand side indicate the zero reference for channel 1 and channel 2 respectively.

I am also guessing that the blue arrow on the right-hand side is the trigger level. At the moment it is at the bottom. It needs to be halfway between the top and bottom of the indicated signal.

I also notice that the coupling is AC. This needs to be DC for both channels!

See if you can make those changes.

Dave

Last edited: