I think I have found the issue. It is with the memory board (well, the Dazzler DMA cycle is not compatible with the operation of the memory board).

Hugo, can you check my logic please?

It would seem that the memory board is equipped with SN74LS375 quad latches on address bus A0 to A15.

The clock (on pins 4 and 12) of these ICs is required to go HIGH to latch what is on the S-100 address bus into the latches so that the memory on the card can be addressed.

This pin is sourced from the logic embedded inside 6C (so I can't see what it is).

The Dazzler DMA cycle sets up by 'forcing' the S-100 control signals to a fixed value and then just cycles through the requisite addresses by changing just the S-100 address bus and not the S-100 control bus.

I don't see a clock being fed to IC 6C, so I suspect that the address latches will latch in whatever rubbish happens to be on the S-100 address bus when the DMA cycle starts. This will invariably be FFFF...

Gut feeling is this memory board is not compatible with the Dazzler...

Having just written this post, I have reread the data sheet and it looks like the 'latch' pin is a logic HIGH level. So if this pin is held HIGH, the SN74LS375 should go 'transparent' - so this 'should' work now...

A second opinion required...

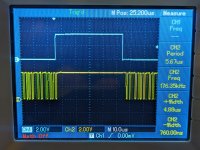

The strobe line is active LOW. As a result, the latches will be transparent UNTIL the /DATA STB signal goes LOW. At this time, whatever is on the S-100 address bus will be latched.

In order for the latched address to be updated, the /DATA STB signal must go HIGH then LOW for the next address. If the S-100 control signals never change state, and there is no clock involved, this will not happen.

The S-100 address bus may not be driven by the Dazzler at the time it takes over the S-100 bus and drives the control lines to a permanent memory read cycle.

A third opinion required now!

Dave