The question is, which of the following is the case:

Possibility #1: 8253 is good, but the signals/address/data to it is bad; or

Possibility #2: 8253 is bad; or

Possibility #3: 8253 is good, signals/address/data to it are good, but the data out of it is being 'damaged' on its way to the CPU.

I know that you are waiting for the replacement 8253 to arrive.

For certain signals, a logic probe or oscilloscope gives confidence, but there times when one needs to go deep, using something like a logic analyser. I know that you have one of those.

Regarding possibility #1. The following procedure is a way of using your logic analyser to investigate 13 pins of possibility #1. You may be forced to do that if the arriving 8253 does not fix the problem. You may wish to try the procedure now.

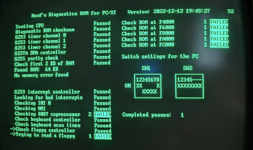

Basically, I have written some small code to go into a ROM. The code will result in activity on the /CS pin, the /WR pin, the two address pins, and the eight data pins. A logic analyser will show the activity, in particular, the timing relationships. Included below is a capture from my logic analyser.

-----------------------------------------------------------------------------------------------------------------------------------

1. Get the ZIP file at [

here], which contains multiple files.

2. Program file 8253_428.BIN into a 2564, then fit that to the 5150 motherboard.

3. Have your logic analyser monitor the following 8253 pins:

- /CS pin,

- /RD pin,

- /WR pin,

- The two address pins,

- The eight data pins.

4. Do a capture. You are expecting to see what is shown in file 8253_428.PNG, with my comments on that as follows:

- What my code is doing is shown in file 8253_428.ASM

- /CS can be seen to be periodically asserted, i.e. the 8253 is periodically being 'selected'.

- /RD is never asserted (my code is doing no I/O reads).

- /WR can be seen to be periodically asserted, and at the time that the 8253 is selected (i.e. my code is doing I/O writes to the 8253).

- The state of the address and data lines is only relevant a short time after /WR is asserted. See the data sheet if required.

- The 8253 can be removed during all of this; we are not programming it to do anything, just seeing if certain inputs are getting to the socket pins.

-----------------------------------------------------------------------------------------------------------------------------------

A further test (of a few) would be to be use code that reads the 8253, expecting to see the /RD pin being asserted during the time that the 8253 is 'selected'.