Hello everyone,

I know this thread has been inactive for a while, I came across it in a search for how to get the logic from PAL16L8 ICs, specifically U87 and U130 in the IBM 5170.

I'm doing a project to design my own recreation of an 5170-alike PC mainboard.

The thread can be found here for anyone interested.

First of all my thanks to newold86 and eeguru for the work you have done and shared here so far. There is no useful definitive information about U87 and U130 to be found anywhere as far as I know, so your information is at least the closest source to be found at the moment. Which is why I posted here in the hope that the definitive versions could be finally known to those who seek this information and come across this thread.

As the thread concluded so far up to now there was the issue remaining that the equations assembled so far were not complete.

This will be due to the complexity of the PAL programming as done by IBM originally, which may make finding the original logic more difficult than the straight evaluation methods we can find from various sources. There is some mention of this problem on various websites pointing this out that in certain types of PAL programming there may occur some fast flipping of outputs which trigger internal changes in the logic states for example.

At first I had some high hopes that reading a PAL as an EPROM with some additional resistors could yield the logic, however right now after doing further reading on the subject I am not entirely hopeful that this may lead to the complete logic as programmed originally. Though there may still be some partial clues to the logic that can be concluded from the equations shared in this thread. I did not crosscheck these equations in this thread yet with my own work and research, which I probably should do before my project proceeds to further stages, I plan to.

I have studied a few sources of information and first found some clues about U130, from a functional perspective to find descriptions of what is expected to happen inside U130, which can be somewhat deduced I believe by what I found. So far I got some information from the VLSI datasheet of the VL81C101B AT chipset IC and from some schematic photos of the Copam PC-501 Turbo PC. Combining all the information so far, I was able to compose an approximation of the logic.

A few cautions, using this info is at the sole risk of the user, there are no guarantees if this will even work at all, maybe it doesn't. Only attempt to use it for anything if you are experienced in doing this type of work and accept the risk of breaking stuff in the process. That's a general comment I want to state here. I will be testing this and other solutions in the interest of my ongoing project.

The VLSI datasheet has documented some useful timing constraints which may be relevant in the circuits and logic IC families that could possibly provide a functional coprocessor/CPU control method, which is what U130 is involved in. I will be testing my best effort version after doing a lot more research and checking against the PAL IC itself to see if the logic is indeed behaving in a similar way. I will probably wire up some switches and LED outputs to be able to see what happens if I assume the logic to be what I share here. Not that this setup can reveal all possible problems but at least it may give me some more confidence.

I have attached a useful page from the VLSI datasheet showing the timing of the /ERROR condition when it occurs, and is cleared by a 287_RESET being asserted.

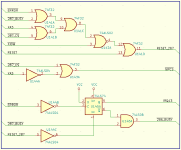

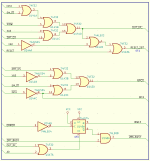

The other attachment shows what the circuits might possibly look like.

The logic types are not conclusive and neither are the gates used, this is just a first attempt to at least compile things in some circuits for starters.

For example the RESET action on the 74LS74 may need additional logic for synchronization or timing delays, which also applies to other areas.

I saw some numbers of 35ns in the VLSI datasheet which seems long and definately in some areas the preference may be to use LS or other slower logic.

So some experimentation may be needed to get it right, such as swapping gates or adding more gates in between, even if the logic is functionally correct.

Needless to say, I will be pushing on in my project which has a huge amount of work to be done.

I will post more in the future in the previously mentioned thread of my project, and PAL related stuff I can share here in this one if anyone is interested.

As mentioned before, it's puzzling that this PAL info is not yet known, and I believe such a brilliant design by IBM really deserves to be preserved, the way I see that to be possible is at least to document the technology completely which my project will certainly attempt to do in my own way.

This is what I have so far, I am sharing everything I find with the community and my 80286 PC project based on the 5170 concept will be published on GitHub as soon as it is completed.

I believe in sharing knowledge and pooling efforts together which is to me the best way that great things can be achieved by us.

If anyone has some comment or useful info please share it here, I would appreciate any and all help!

Kind regards,

Rodney