Multiple presses of your reset button (shorting out C68) just causes the CPU to "have another go" at trying to correctly execute the PETTESTER code. My educated guess is that sometimes the CPU halts after a short while, but (sometimes) it manages to get far enough to display something useful on the video screen to let you think it is working - but then the CPU halts again...

This would usually indicate a faulty IC socket or bad soldering, PCB track or something similar.

However, it could also be an IC 'on the edge of operation' or some sort of resistive, capacitive or inductive effect between (say) the data or address bus lines. However, in this case, you can't analyse this sort of problem with the whole PET - you have to break the problem down into smaller (and more manageable) 'chunks'.

Randomly removing ICs and testing them will probably not indicate this sort of issue at all. The IC testers only (generally) check the logic function and not the timing of the ICs. For this type of test equipment you would be paying tens of thousands of dollars!

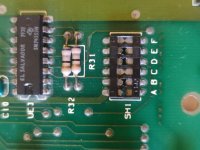

This is what we were attempting to do last night. Remove all of the influences on the data bus by removing the VIA, PIAs, ROMs and the buffers E9 and E10 and using eight off 1k resistors to simulate a NOP instruction on the data bus itself. If this works RELIABLY we can then move on to the next step of our analysis - having removed the data bus itself from our list of things to check...

Dave