jon1967us

Experienced Member

I will also resume attempting to test the Phantom waveforms as you previously suggested.

| VCF West | Aug 01 - 02 2025, | CHM, Mountain View, CA |

| VCF Midwest | Sep 13 - 14 2025, | Schaumburg, IL |

| VCF Montreal | Jan 24 - 25, 2026, | RMC Saint Jean, Montreal, Canada |

| VCF SoCal | Feb 14 - 15, 2026, | Hotel Fera, Orange CA |

| VCF Southwest | May 29 - 31, 2026, | Westin Dallas Fort Worth Airport |

| VCF Southeast | June, 2026 | Atlanta, GA |

I did this and verified that signals on the cpu address pins are echoed on the outputs of buffers U68,81,67. Everything looks good to be to this point.I would now check the other side of the address buffers to make sure these are OK next.

I suspect your logic probe would have difficulty resolving these signals in the first place. I suspect it to be the wrong tool for the job I am afraid.

Dave

Yep, the jumper’s installed.On your Sol, be sure the Phantom jumper is installed (F-G)

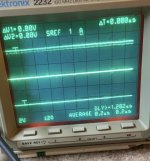

Enable channel 1 and channel 2 on the scope

Set vertical scale for both channels to 2v/div and time scale to 200 or 250ns/div.

With auto trigger selected, position channel 1 near the bottom of the top half of the display and channel 2 near the bottom of the bottom half of the display.

Change to normal trigger, falling edge, at about 2v on channel 2

Connect channel 2 to RESET on U63p9, or the side of R50 connected to this pin.

Connect channel 1 to the positions listed below, one at a time, for each test run. A test run is initiated by activating RESET from the Sol-20 keyboard.

Get screen shots of each of the following test points as RESET is released. You may have to move your horizontal Trigger position towards the left edge of the display.

U24p1

U24p2

U22p3 or p11

U34p11

Mike

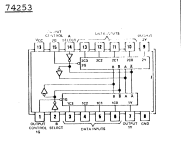

Haven’t replaced it yet since I don’t have any spare 74ls253 on hand. Have some on order that should arrive shortly. Btw, any recommendation for a vendor for chips, other than eBay? Mouser doesn’t carry many of the older ic packages, it seems.U66 is responsible for the data input multiplexing (the top 2 data bits) to the CPU. If this is defective (and you say you have checked it on a chip tester) have you replaced it yet?

I assume most (if not all) of your ICs are in sockets?

There can be other reasons for these pins to be anomalous - but if a (working) chip tester says it is duff - then it probably is. However, it could also have died as a result of another fault - although this would be fairly difficult for a piece of TTL logic (unless the pins were connected to a source of volts that were fairly low impedance (or outside of tolerance)).

Dave

It was probably nothing you did. 74 series TTL can just fail spontaneously, I have had a number do it over the years, typically when I was using the equipment, so they were not really stressed by anything in particular. Something goes awry inside the die with internal corrosion or propagating micro- fractures damaging the circuit. I think Daver-2 does a lot of research on this and even has IC's de-capped to find out "what went wrong".Well, I went to the local electronics store and lo and behold they actually had 74LS253 in stock. Subbed it into U66 and presto, my prompt has returned.

So, the question of how/why it failed is still something to keep an eye on. It may have gotten compromised when I initially removed and cleaned all of the ICs and sockets.

Still would like to figure out how to do the dual trace/trigger/storage on my scope, so I’ll continue to play with that.

Continuing to test function and loading programs for now.