Dave,

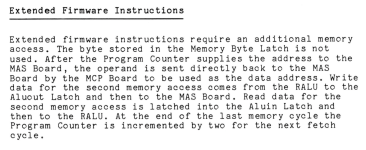

I think Tektronix called ALL the "NEW" 4052/4054 and 4052A/4054A opcodes Extended - see this page in the 4052A Assembler doc:

Therefore - this has NOTHING to do with the opcode addressing mode - which is exactly the same as the 6800 - including the A-Series opcodes that require a C7 or FC prefix byte.

The Assembler document lists the processor opcode addressing modes for each of the new opcodes - same as a 6800:

4052/4054 and 4052A/4054A Addressing modes (same as 6800):

ACC - Accumulator

In accumulator addressing, either accumulator A or accumulator B is specified. These are 1- byte instructions.

Ex: ABA adds the contents of accumulators and stores the result in accumulator A

IMM - Immediate

In immediate addressing, operand is located immediately after the opcode in the second byte of the instruction in program memory (except LDS and LDX where the operand is in the second and third bytes of the instruction). These are 2-byte or 3-byte instructions.

Ex: LDAA #$25 loads the number (25)H into accumulator A

DIR - Direct

In direct addressing, the address of the operand is contained in the second byte of the instruction. Direct addressing allows the user to directly address the lowest 256 bytes of the memory, i.e, locations 0 through 255. Enhanced execution times are achieved by storing data in these locations. These are 2-byte instructions.

Ex: LDAA $25 loads the contents of the memory address (25)H into accumulator A

EXT - Extended

In extended addressing, the address contained in the second byte of the instruction is used as the higher eight bits of the address of the operand. The third byte of the instruction is used as the lower eight bits of the address for the operand. This is an absolute address in the memory. These are 3-byte instructions.

Ex: LDAA $1000 loads the contents of the memory address (1000)H into accumulator A

IDX - Indexed

In indexed addressing, the address contained in the second byte of the instruction is added to the index register’s lowest eight bits. The carry is then added to the higher order eight bits of the index register. This result is then used to address memory. The modified address is held in a temporary address register so there is no change to the index register. These are 2-byte instructions.

Ex: LDX #$1000 or

LDAA $10,X

Initially, LDX #$1000 instruction loads 1000H to the index register (X) using immediate addressing. Then LDAA $10,X instruction, using indexed addressing, loads the contents of memory address (10)H + X = 1010H into accumulator A.

INH - Implied (Inherent)

In the implied addressing mode, the instruction gives the address inherently (i.e., stack pointer, index register, etc.). Inherent instructions are used when

no operands need to be fetched. These are 1-byte instructions.

Ex: INX increases the contents of the Index register by one. The address information is "inherent" in the instruction itself.

INCA increases the contents of the accumulator A by one.

DECB decreases the contents of the accumulator B by one.

REL - Relative

The relative addressing mode is used with most of the branching instructions on the 6802 microprocessor. The first byte of the instruction is the opcode. The second byte of the instruction is called the

offset. The offset is interpreted as a

signed 7-bit number. If the MSB (most significant bit) of the offset is 0, the number is positive, which indicates a forward branch. If the MSB of the offset is 1, the number is negative, which indicates a backward branch. This allows the user to address data in a range of -126 to +129 bytes of the present instruction. These are 2-byte instructions.

Ex:

PC Hex Label Instruction

0009 2004 BRA 0FH

___________________________________________

Since the 4052/4054 have A and B 64KB address spaces - each of which can have executable code in one space and data in the other space, that does blur the 6800 addressing modes descriptions above since the word "memory" in the 6800 is anywhere in the 64KB memory space (RAM and or ROM).

IMM mode for 4052/4054 is clearly describing the operands follow the instruction in the same SPACE as the instruction.

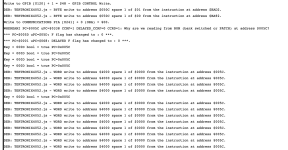

DIR mode on the other hand appears to always require access to the RAM space A for the reads and writes. And the default CC bits Fetch from B and Data in A

EXT parameters are an executable address - so must come from the FETCH space - which could change if the Fetch CC bit previously changed.

I think your microcode emulator needs to exactly match the 2901's and hardware on the boards