sergey

Veteran Member

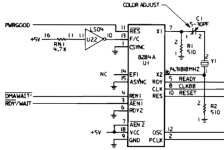

In post #1 is, "I have traced F/C going from the 8284 to pin 12 of the 74LS27 ..."

That doesn't really say anything. For example, in IBM XT the F/C pin is tied "low" through an inverter gate. It is quite possible that a 74LS27 gate is used to produce a constant logic "high" or "low"...

The glitch free clock switching circuit requires both input clocks to be running. If one of them stopped, the switching circuit might not function properly...Clearly 14.31818MHz aren’t getting generated (not sure why) and I am not getting anything significant over on EFI. I guess that means the switching circuit is out of order?

So, I would investigate why 14.31818 MHz clock is not being generated first.

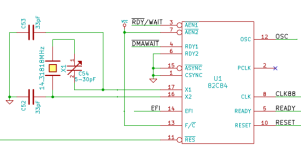

It appears that your board is using 82C84. Please note that the oscillator circuit for the original (supposedly TTL-LS) 8284 and CMOS 82C84 are different.

You can't simply switch these ICs, without modifying the clock circuit. Particularly, 82C84 needs load capacitors connected between the crystal pins and the ground, while 8284 has two 510 ohm resistors there instead.

Refer to the IBM XT schematic above for the 8284 crystal connection.

Here is the schematic for the 82C84:

The CLK and PCLK look good for a 24 MHz crystal. It is quite possible that your LA cannot sample 24 MHz frequencyCLK is 8MHz. PCLK is 4MHz. EFI looks weird? Maybe it’s because the 24MHz oscillator is too high for my LA?