Checked it all again and it looks good, at least until someone else finds the next bug.

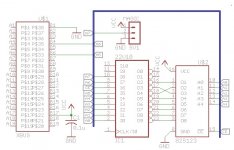

One thing for you to check - A7 on the 82S147 was tied to GND, and A8 was the bank select jumper. On the new card the bank select jumper is A7, and there is no A8. If you got that right, then it should be good.

Digger, I reread your original post, and I want to check one thing:

IIRC the onboard video can be disabled with a DIP switch, though it may need a newish ROM. Is there some other chip we need to clone to make this thing work?

One thing for you to check - A7 on the 82S147 was tied to GND, and A8 was the bank select jumper. On the new card the bank select jumper is A7, and there is no A8. If you got that right, then it should be good.

Digger, I reread your original post, and I want to check one thing:

It consists of a card and a separate disabler chip for the on-board video board.

IIRC the onboard video can be disabled with a DIP switch, though it may need a newish ROM. Is there some other chip we need to clone to make this thing work?