Marty

Veteran Member

Hi All;

Daver, Thank You for Your Response, and answers..

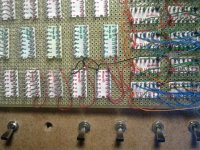

"" I have been comparing various sources of the list of ICs tonight and most of the sources agree - but one thing that jumps out to me is that there are more logic chips on the photograph of the wire-wrapped board than are in the kit.

One possibility that could account for the difference is that the board in the photograph has the memory expanded to a full 4K. I have been ignoring the memory devices themselves - but I am wondering if there are any additional 74XX series logic accompanying the memory expansion. I will check this out later. ""

Yes, the Extra Ic's are for Both the Memory and the I/O Serial Port..

It uses 48 each 2102's just for the memory, along with other support Ic's, and another bunch for the I/O..

"" I have also been identifying 'issues' on the schematic diagrams (e.g. unconnected input pins such as clocks, /preset, J and K inputs etc.). When I have checked the wiring lists though - they are correctly connected. The outcome is that if you are following the schematics for wiring then you will be mislead (i.e. some critical inputs will be left floating - and hence little antennas for picking up noise). If you are following the wiring lists themselves - you should be OK. ""

I wired from the ExtSorted List, and not the Schematic..

There are things that are Not in the Schematic, that are in the WireList.. Like all of the Muxes, what is in the Schematic, is only a Partial Schematic of the Mux circuitry, along with the Registers..

"" handling INDIRECT operands and the like - or rather generating the sequence for such processing. ""

That is what I need the most at the present..

"" I will write up a description of it later when I am not too tired (it is pretty late in the UK now). "" That's fine..

"" I won't answer your NAND gate query above at this late hour - I will only screw up the Karnaugh Map! "" That's fine..

THANK YOU Marty

Daver, Thank You for Your Response, and answers..

"" I have been comparing various sources of the list of ICs tonight and most of the sources agree - but one thing that jumps out to me is that there are more logic chips on the photograph of the wire-wrapped board than are in the kit.

One possibility that could account for the difference is that the board in the photograph has the memory expanded to a full 4K. I have been ignoring the memory devices themselves - but I am wondering if there are any additional 74XX series logic accompanying the memory expansion. I will check this out later. ""

Yes, the Extra Ic's are for Both the Memory and the I/O Serial Port..

It uses 48 each 2102's just for the memory, along with other support Ic's, and another bunch for the I/O..

"" I have also been identifying 'issues' on the schematic diagrams (e.g. unconnected input pins such as clocks, /preset, J and K inputs etc.). When I have checked the wiring lists though - they are correctly connected. The outcome is that if you are following the schematics for wiring then you will be mislead (i.e. some critical inputs will be left floating - and hence little antennas for picking up noise). If you are following the wiring lists themselves - you should be OK. ""

I wired from the ExtSorted List, and not the Schematic..

There are things that are Not in the Schematic, that are in the WireList.. Like all of the Muxes, what is in the Schematic, is only a Partial Schematic of the Mux circuitry, along with the Registers..

"" handling INDIRECT operands and the like - or rather generating the sequence for such processing. ""

That is what I need the most at the present..

"" I will write up a description of it later when I am not too tired (it is pretty late in the UK now). "" That's fine..

"" I won't answer your NAND gate query above at this late hour - I will only screw up the Karnaugh Map! "" That's fine..

THANK YOU Marty

Last edited: