Thanks.

What you are posting in #2,051 is not really possible then...

Can you use your logic probe and check the data levels on each pin of UD9 and post back the results please.

Can you also measure the DC voltage (using a digital multimeter) at the actual UD9 ROM itself (black lead to pin 12 and red lead to pin 24).

Can you also measure the DC voltage on the /CS line (using a digital multimeter) at the actual UD9 ROM itself (black lead to pin 12 and red lead to pin 20).

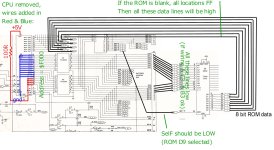

Then double-check (with the logic probe) the logic levels on the CPU socket pins 33, 32, 31, 30, 29, 28, 27 and 26 again.

You have checked the continuity from the CPU data bus pins to the ROM data bus pins. You haven't detailed the actual resistance though. That would be useful to know. Should be < 1 Ohm. So, there should be absolutely no reason why the logic levels on the UD9 ROM data bus are any different to those on the CPU socket. If they are - there is something strange going on. But what...

Dave