Hugo Holden

Veteran Member

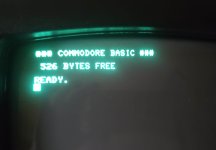

Daver2.... It is very interesting that the byte which codes a Break is 00.

I just performed an interesting experiment on the CPU in my pet. When the CPU's data pins are left open DA0...DA7, they assume a low state and would be read by the CPU as low not high.

If there was a failure in the gating that controls the 74LS244 E9 & E10, which strobes the bus data onto the CPU (via the CPU R/W pin 34 of the CPU & buffer A10 and gate A5) the output of the 74LS244 would go into a high Z state when it should be transferring data to the CPU, the CPU would then execute a BRK as it would read an 00. ( also gates A3 & B2 would need checking).

Obviously if all that gating was working it could be reading a genuine 00 from the data bus, which could be corrupt (intermittent firmware- those over-voltaged 2532A's), or possibly PIA'a interfering but I think the pettester crashed with the PIA's out so probably not them, assuming that this is the same fault that caused the pettester to crash.

I just performed an interesting experiment on the CPU in my pet. When the CPU's data pins are left open DA0...DA7, they assume a low state and would be read by the CPU as low not high.

If there was a failure in the gating that controls the 74LS244 E9 & E10, which strobes the bus data onto the CPU (via the CPU R/W pin 34 of the CPU & buffer A10 and gate A5) the output of the 74LS244 would go into a high Z state when it should be transferring data to the CPU, the CPU would then execute a BRK as it would read an 00. ( also gates A3 & B2 would need checking).

Obviously if all that gating was working it could be reading a genuine 00 from the data bus, which could be corrupt (intermittent firmware- those over-voltaged 2532A's), or possibly PIA'a interfering but I think the pettester crashed with the PIA's out so probably not them, assuming that this is the same fault that caused the pettester to crash.