Will an IBM 51X0 system count up only to the amount of RAM that it is able to address?

To clarify, if one address line was severed or not connected, would that drop the amount of memory detectable by the system (like the cheap 16kbit memory, which was actually faulty 32kbit, but still worked) that Sinclair used in the 1980s, or would that break the system entirely? This is assuming that there's some kind of POST failsafe in the BIOS that drops the amount of addressable memory to a power-of-2 or divisible amount and ignores the faulty RAM beyond that point. (i.e. 512kbyte of RAM, but 128k is not properly addressable [maybe 16k does not work], so it drops to 384kbytes.) Of course, I may just be spitting smoke.

Long and short of it is no, not unless the computer is equipped for such a situation in hardware. I'll try to explain momentarily.

I seem to have found an address line (A17) that may not be connected to anything, and may be my problem. (It's not connected to any 37x, 24x, or 138 logic chips.) I'm not sure yet, though. I'll have to continue probing with the multimeter in order to find out.

Maybe it's part of your problem, but it's not your whole problem. But let's start here:

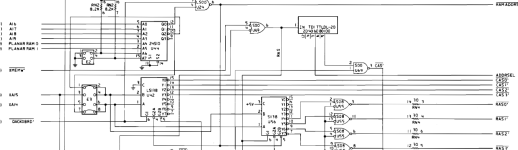

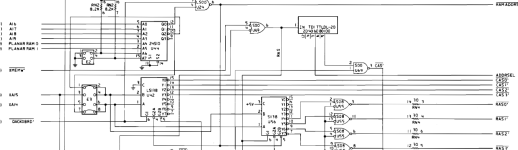

As laboriously gone over earlier, U84 on this snippet from the IBM 5160 motherboard schematic is one of the (important) differences between this board, which supports 256kbit RAMs, and the (later version of) the 5150, which only supported 64kbit. Again, rehashing what we already know, it's a multiplexer with two used inputs, XA16 and XA17, buffered versions of the CPU's A16 and A17, and the output derived from them is MA8, which is connected to pin one of all the memory sockets. The input "ADDRSEL" is used to switch which input appears on the output depending on which part of the RAS/CAS cycle we're on. Two address lines is two bits, the number of possible combinations in two bits is four, so if everything is working right the addition of this part is what lets the same sockets hold four times as much memory; a line that's unused on 4164 chips turns into (effectively) two additional address bits. This means, tada, the same array covers 18 address bits (2^18, 256K, instead of 2^16, 64k).

So... obviously, this is a problem if A17 isn't connected to this multiplexer; it means that either RAS or CAS will always present the same value to A8, and this reduces the total size of the memory bank to 128k. If the memory *addressing circuitry* were set up to expect 256k in a bank this isn't a "self-healing" problem, one half of the 256k range of that bank will just address a duplicate of the other because of the stuck bit. In some hypothetical situation where you were sitting on a pile of 41256s that you knew all had the same half of the chip "bad", sure, you could take advantage of this by going ahead and populating those chips into banks and setting up the address circuitry accordingly. (Per your reference, they actually did this with half-bad 16K 4116 chips back in the late 1970's; they sold them as "4108s" and they were used in Commodore PETs, among other things.) But I absolutely 100% don't think this is what's happening in your Sanyo. Full stop.

If you have a logic probe or oscilloscope I would by all means suggest you probe the "XA16" and "XA17" inputs on the '158 multiplexer you added to control A8 to see if they're changing; if you see XA16 pulsing and XA17 not pulsing then you know, full stop, that the 256K banks will not work, and that's useful information, but whether they're pulsing or not I'm am positive that it doesn't matter, your memory decoder isn't set up to make use of the full capacity of these banks. Even if everything is working here I think you're only set up to use a quarter of the capacity of the 256K banks, the only thing having this circuitry working is going to change is

which quarter you're using in each bank.

Here's another screenshot from the 5160 schematic. Completely forget about the memory array right now, full stop, other than this: Each row of sockets are all wired in parallel except the CAS/RAS lines. It is the CAS/RAS line activity that triggers read/write/refresh cycles on the chip:

See how A16-A19 feed into that 24S10 chip (and some lines that go to DIP switches and jumpers, but we're ignoring those right now), and three control lines come out. The 24S10 PROM programmed with a bitmap of information so for a given memory address (with 64K granularity, because it only sees the top four address lines, letting it break the full 1MB of address space into 16 chunks) it activates some combination of output lines. The first, "RAMADDRSEL", comes on if ANY memory on the planar is supposed to be active; it controls the buffer in front of the memory chips which asserts control of the bus if it thinks the memory chips should be answering the bus request. The other two lines coming out of it are a two bit bank select. Based on the memory address one of four bank numbers 0 through 3 will come out of these lines.

It is the programming of this PROM that "knows" if a bank is supposed to have 256k or 64k in it, and what areas of the memory map that bank is going to cover.

The bank output from PROM goes to that pair of LS138s labeled U42 and U56, which decode the "multiplexed" binary number into a singleton CAS0-3 or RAS0-3 signal. They're 1-of-8 selectors (of which half of each is being wasted, turning them into 1-of-4 selectors) so only one memory bank will get an active CAS/RAS at a time. Thus... and there's the part I keep repeating:

It doesn't matter if you fixed up the memory bank so it's "256K big" instead of "64K big" if this part of your Sanyo doesn't know about it. As it came from the factory your Sanyo was set up so it broke the first 256K of the 1MB address space into four 64K chunks, and activated a separate CAS/RAS pair for each of those chunks. If you haven't adjusted that and just substituted 256K chips in the bottom two banks, again, even if everything is working perfectly in that area here is what your memory map is going to work out as at a hardware level:

0-64K: provided by the

first 64k of the 41256s in bank0. (

A8 will be zero on both CAS and RAS)

64k-128K: provided by the

second 64K of the 41256s in bank1 (

A8 one on RAS, zero on CAS)

128k-192k: provided by the 4164s in bank2. (

A8 zero on RAS, one on CAS, the 4164s don't care about A8, return the same 64k regardless)

192k-256k: provided by the 4164s in bank3.

(A8 one on CAS and RAS)

Unless I missed the part where you redid this part of the circuitry all the fooling around in the world with the memory banks themselves isn't going to change when they're enabled. Now, sure, in some later computers the computer can figure out itself what size memory chips are installed in a bank and switch to a memory addressing scheme that suits it, but I absolutely guaruntee your Sanyo doesn't have that implemented. (The 5160 doesn't either; it can guess if a bank is populated but it can't change its addressing behavior if you stick the wrong size into a bank.)