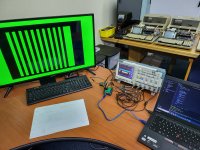

Got a couple of PET monitors to repair. To make this easier on the bench, the idea is to make a circuit that will generate a video pattern, allowing the monitor to be repaired without having a PET motherboard involved.

/full disclosure: The last time I worked, in any anger, with analogue monitor/TV signals was in the early 80's as a junior tech at the local broadcast corporation. Whatever I knew then have long since been lost in the mist of red wine.

Whatever information forum members can share on how to generate the correct signals for both the 9" and 12" monitors, would be greatly appreciated.

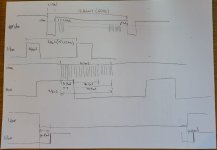

Using information @Hugo Holden posted, together with measurements I did on a working 2001, I got the following for the 9" display:

.

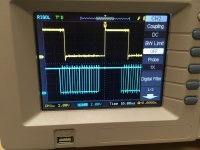

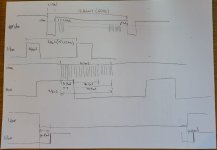

- V-Sync: A negative pulse of 1.25ms, every 16.667ms (60Hz)

- H-Sync: A positive pulse of 24us, every 64us (15.625KHz)

Observations from looking at the 2001:

.

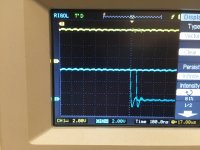

- H-sync seems to go high, about 4.8us after V-sync goes low. I'm not sure if this is required or an artifact of the PET circuit.

- Video seems to start about 20us after H-sync goes high.

- A full line of video seems to be about 40us.

.

.

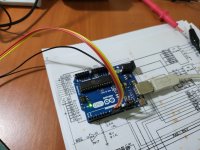

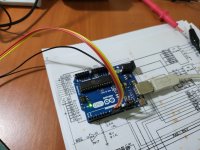

Using the above, I made a signal generator using an Arduino. It seems to "mostly" work but really because it was a monkey-see, monkey-do effort, not because I know what I'm doing. Getting a lot of artifacts and what looks like "analog noise" but must be some errors in generating the signal.

.

Couple of questions:

.

- Horisontal is not a multiple of Vertical; how does one keep them in sync? Is it necessary to keep them in sync?

- Should V and H start at the same time? I measure that H triggers about 4.8us after V. Is this correct or can they start at the same time?

- Where, in all of this, should the video signal be generated?

Any info would be greatly appreciated.

/full disclosure: The last time I worked, in any anger, with analogue monitor/TV signals was in the early 80's as a junior tech at the local broadcast corporation. Whatever I knew then have long since been lost in the mist of red wine.

Whatever information forum members can share on how to generate the correct signals for both the 9" and 12" monitors, would be greatly appreciated.

Using information @Hugo Holden posted, together with measurements I did on a working 2001, I got the following for the 9" display:

.

- V-Sync: A negative pulse of 1.25ms, every 16.667ms (60Hz)

- H-Sync: A positive pulse of 24us, every 64us (15.625KHz)

Observations from looking at the 2001:

.

- H-sync seems to go high, about 4.8us after V-sync goes low. I'm not sure if this is required or an artifact of the PET circuit.

- Video seems to start about 20us after H-sync goes high.

- A full line of video seems to be about 40us.

.

.

Using the above, I made a signal generator using an Arduino. It seems to "mostly" work but really because it was a monkey-see, monkey-do effort, not because I know what I'm doing. Getting a lot of artifacts and what looks like "analog noise" but must be some errors in generating the signal.

.

Couple of questions:

.

- Horisontal is not a multiple of Vertical; how does one keep them in sync? Is it necessary to keep them in sync?

- Should V and H start at the same time? I measure that H triggers about 4.8us after V. Is this correct or can they start at the same time?

- Where, in all of this, should the video signal be generated?

Any info would be greatly appreciated.