You are aware that an 8088/8086 bus cycle is four clock cycles...

I was aware that there was a 4 clock timing of the read/write operations although I thought it was based on a clock 4x the CPU clock. I must have misunderstood something when poking around on the Tandy 1000 board.

I wrote a little test program to do rapid register writes and explored a bit with the scope. I used a 486 DX2/66 with ISA clock set to 33/3. The chipset seems to drop this to 10Mhz by extending some of the cycles. I used this as I expect there will be 10MHz bus clocks on some of the 286 boxes. I have shared one image here, slightly more info is available at https://github.com/JayesonLS/8bit-ide-analysis

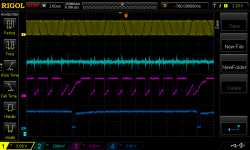

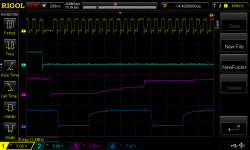

This image is shows about the first 1.5 IO write cycles of the ST05X BIOS code that does 6 rapid writes to port 320 to set the controller command registers. Yellow = CLK, cyan = XTA ~CS, magenta = D0, blue: ~IOW. The scope is not calculating the frequency of CLK well in this image - zooming out a bit seems to give a fairly consistent 10MHz. One interesting thing with the 486 is that the CS gets held low for long periods. I think the address lines do not always get updated on the ISA bus, which I guess makes sense since it is not possible to keep the slower ISA bus fully up to date with what is happening on the CPU bus. One thing I note is that the IO write (and presumably read) cycle seems to be even longer than 4 clocks. It does sound familiar to me that IO cycles are extended.

I also ran a routine that uses REPNZ OUTSB and the timing is identical on this 486. I think I am going to have to run these tests again on a 286 to see what happens. I do have a Tandy 1000 TL/2 which seems like a good fit other than the 8MHz CPU. Hopefully I will come across a 10MHz 286 XTA PC somewhere along the way.

Anyway, the data point I was after is that there is 13 clocks between each ~IOW. I was hoping it would be just a little longer but it think it work for what I have in mind. My hardware plan was to use at ATMEGA328 at 20MHz with an external universal shift register to hold the data. And a GAL22v10 to provide some glue. I like this approach as the bill of materials is inexpensive, can be all through hole and anyone with a TL866 can program the chips. Plus the timings on these micros is quite predictable.

The idea is that on an IO write, the GAL would latch the data into the shift register and signal the ATMEGA there was data. The ATMEGA would then trigger an SPI read. The SPI read would take 8 10MHz bus clocks to get the data out of the shift register, leaving at most 5 10Mhz clocks / 10 20Mhz clocks for the ATMEGA to detect the signal from the GAL and trigger the SPI read. I think it will just work. Especially if there is a requirement to use lower bus clocks if someone, for some reason, wanted to use an XTA card in a fast PC.

[EDIT] I set the 486's bus clock back to the default 8.33MHz. The period between ~IOW's is still 13 CLK's which gives an additional 5 20MHz clocks to the ATMEGA. I am excited - I think my plan is going to work.

Last edited: