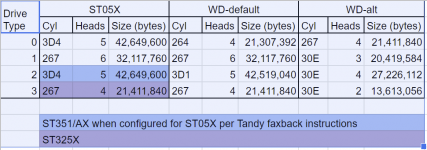

Umm, wow! Nice drive collection. Those WD's sound just wonderful in my opinion. When mine feels like working it is a happy day. I understand the desire to be able to use them.

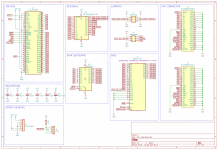

I think Eudimorphodon is right that it would probably best to design a new card to make use of an original BIOS. It is not a complicated board. I expect you could actually run the WD BIOS on the Seagate card and vice versa. I was thinking I would design a card after the drive replacement was done. I thought some folks might want to be able to run a period bios. I kind of want to put one together right now. It would not take very long to do the schematic. I keep getting more pedantic in my board layouts with each new one I do, and so there is probably a solid couple of days of layout work to do.

I do have my XT-IDE CF variant to start with: https://github.com/JayesonLS/ISA-Cards#cf-combo-super-lite-1-2

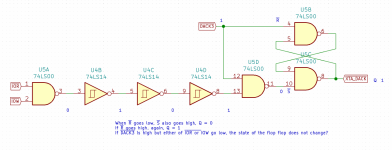

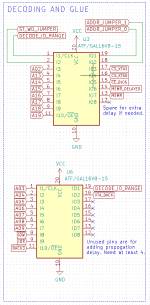

Going the opposite way... could it be possible to add support for 8-bit IDE-XT drives to a modern XT-IDE interface card? The IDE-XT interface cards, like the Western Digital WD-XT150 shown below, are all very simple, with just a few off-the-shelf 74LS-series chips and a ROM.

[/IMG2]

I think Eudimorphodon is right that it would probably best to design a new card to make use of an original BIOS. It is not a complicated board. I expect you could actually run the WD BIOS on the Seagate card and vice versa. I was thinking I would design a card after the drive replacement was done. I thought some folks might want to be able to run a period bios. I kind of want to put one together right now. It would not take very long to do the schematic. I keep getting more pedantic in my board layouts with each new one I do, and so there is probably a solid couple of days of layout work to do.

I do have my XT-IDE CF variant to start with: https://github.com/JayesonLS/ISA-Cards#cf-combo-super-lite-1-2