daver2

10k Member

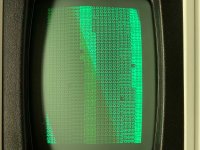

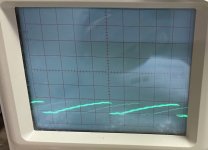

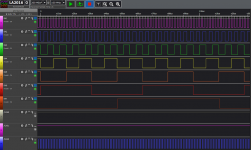

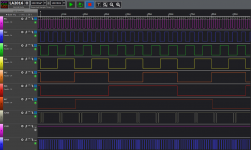

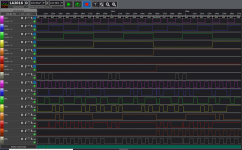

>>> I haven't had a chance to try any of the suggestions, but just wanted to resolve your confusion due to my less-than well-organized post above. The /CS trace above wasn't taken with the NOP generator in place, it was with the CPU set up regularly. I just included it as an example of what I was seeing on the kernal ROM when the board was trying to boot. No activity on the other ROMs.

That's OK - I just want to be clear in my mind under what conditions the various traces were taken under (as this matters in deciphering what we are seeing).

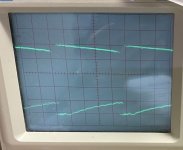

The NOP generator will demonstrate that the CPU/address buffers and chip select decoder is operational - as it doesn't involve the CPU executing instructions out of a ROM (we are forcing the data bus with a NOP = $EA).

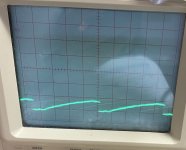

My PETTESTER will demonstrate that the Kernal ROM and PETTESTER ROM will either work or not. If it doesn't work - the next question is what is the CPU actually executing (if anything)?! In this case have a look at the CPU SYNC pin (pin 7). If this pin is not pulsing high (it does this for every CPU instruction executed) the CPU isn't executing instructions at all (or was and stopped) indicating a problem with decoding $Fxxx and/or $Exxx. In this case we can monitor /SEL E and /SEL F - along with SYNC and /RESET (triggering on /RESET) to see what happens for the first few tens of instructions following a reset or power-up condition- and if it goes into the weeds or not.

If the CPU is still executing instructions - is it doing so within $Exxx (PETTESTER) or $Fxxx (Kernal ROM). The first is correct, the second not.

Executing the BASIC ROMS themselves just means that there are plenty of places for it to go into the long grass and die...

Dave

That's OK - I just want to be clear in my mind under what conditions the various traces were taken under (as this matters in deciphering what we are seeing).

The NOP generator will demonstrate that the CPU/address buffers and chip select decoder is operational - as it doesn't involve the CPU executing instructions out of a ROM (we are forcing the data bus with a NOP = $EA).

My PETTESTER will demonstrate that the Kernal ROM and PETTESTER ROM will either work or not. If it doesn't work - the next question is what is the CPU actually executing (if anything)?! In this case have a look at the CPU SYNC pin (pin 7). If this pin is not pulsing high (it does this for every CPU instruction executed) the CPU isn't executing instructions at all (or was and stopped) indicating a problem with decoding $Fxxx and/or $Exxx. In this case we can monitor /SEL E and /SEL F - along with SYNC and /RESET (triggering on /RESET) to see what happens for the first few tens of instructions following a reset or power-up condition- and if it goes into the weeds or not.

If the CPU is still executing instructions - is it doing so within $Exxx (PETTESTER) or $Fxxx (Kernal ROM). The first is correct, the second not.

Executing the BASIC ROMS themselves just means that there are plenty of places for it to go into the long grass and die...

Dave