Nivag Swerdna

Veteran Member

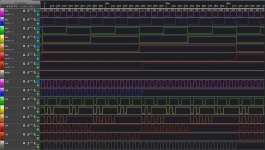

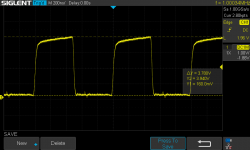

It's easier to see with no CPU. You should just get FA0...FA6 incrementing and nRAS toggling at 2x; that should be enough for refresh. Everything looks fine so far... which is why I keep mentioning voltages...

| VCF West | Aug 01 - 02 2025, | CHM, Mountain View, CA |

| VCF Midwest | Sep 13 - 14 2025, | Schaumburg, IL |

| VCF Montreal | Jan 24 - 25, 2026, | RMC Saint Jean, Montreal, Canada |

| VCF SoCal | Feb 14 - 15, 2026, | Hotel Fera, Orange CA |

| VCF Southwest | May 29 - 31, 2026, | Westin Dallas Fort Worth Airport |

| VCF Southeast | June, 2026 | Atlanta, GA |

Ah OK. Missed that. If these were measured AT the DRAM sockets then fair enough.Post #28 should cover the rail voltages.

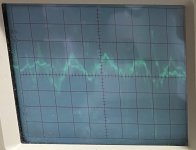

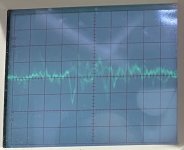

"The +/- 5 and 12 V lines all are very close to the desired value and with about 10 mV of ripple."

It's easier to see with no CPU. You should just get FA0...FA6 incrementing and nRAS toggling at 2x; that should be enough for refresh. Everything looks fine so far... which is why I keep mentioning voltages...

Post #28 should cover the rail voltages.

Worth double-checking them though with an oscilloscope - looking for dc level and ripple/noise.

That should put the rail voltage issue to be fairly quickly.

Can we then look at the data bus in more detail please please?

Dave

My error there... MUXA was working in earlier plots... MUXA will be a bit indeterminate with no CPU fitted as it is partially derived from R/nW output. My bad.I see on an earlier trace that MUXA is flat. That's not good. MUXA is needed to select the row/col.

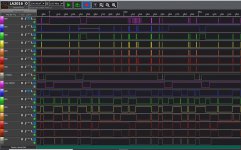

Assuming RDx is the RAM Data, then the logic analyser is indicating potential problems somewhere...

Unfortunately, a logic analyser is no good for looking for this type of potential fault. You need to use a scope.

Can I suggest doing what is in post #47 and I will think about how to proceed on the data bus?

What make and model is your scope? I will see if we can interconnect your logic analyser and scope together...

Are any if your DRAM chips in sockets by any chance?

Dave

I'm starting to think that functionally all the bits are working... and that it is a poor connection. To enable the DRAM you a need a nRAS, nCAS, nWE and the respective supply voltages... all these signals have examples that look correct on the earlier plots. I've run out of suggestions and will stand back for a bit.When I first started troubleshooting this the problem was intermittent and seemed like tilting the board one way or another would cause it to start up seeing the full complement of memory, which makes me suspect a bad solder joint or other poor connection somewhere.

I'm starting to think that functionally all the bits are working... and that it is a poor connection. To enable the DRAM you a need a nRAS, nCAS, nWE and the respective supply voltages... all these signals have examples that look correct on the earlier plots. I've run out of suggestions and will stand back for a bit.

The oscillator is fine. It’s a horrid circuit anyway...

Do you have facilities for programming a 2716 EPROM at all? I suspect what you require is a test program to read and write a value to (say) memory location 0.

Dave

I think they are writing, not reading but all the RAS/CAS etc are OK. Now they would only WRITE not READ if you had a short to ground on nWE... so if I was looking for dodgy connections it would be nWE i.e. the Pin 3s is where I would start.Can anyone suggest a good strategy to find a fault like this?

ORG $E000 ; EDIT ROM for BASIC 4 (no CRTC).

LOOPY:

LDA #$00 ; Load A with 0

STA 0 ; Store A to address $0000

LDA 0 ; Load A from address $0000

LDA #$FF ; Load A with FF

STA 0 ; Store A to address $0000

LDA 0 ; Load A from address $0000

JMP LOOPY ; Keep repeating...

END ; End of test program.E000 .ORG $E000 ; EDIT ROM for BASIC 4.

E000 LOOPY:

E000 A9 00 LDA #$00 ; Load A with 0

E002 85 00 STA 0 ; Store A to address $0000

E004 A5 00 LDA 0 ; Load A from address $0000

E006 A9 FF LDA #$FF ; Load A with FF

E008 85 00 STA 0 ; Store A to address $0000

E00A A5 00 LDA 0 ; Load A from address $0000

E00C 4C 00 E0 JMP LOOPY ; Keep repeating...

E00F END ; End of test program.

LOOPY: E000 DEFINED AT LINE 4

> USED AT LINE 12