Divarin

Veteran Member

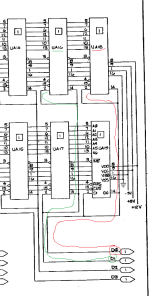

Oh man that took a really long time but the new ram chips finally came in. I replaced UA4 with one of the 8116's. The pattern pettester is giving me looks the same though:

For reference here was what it looked like using the original chip in UA4:

I still expected some bads but not in the same place. I guess I could go ahead and just install sockets for all of the 2nd bank chips, or just take them one at a time.

For reference here was what it looked like using the original chip in UA4:

I still expected some bads but not in the same place. I guess I could go ahead and just install sockets for all of the 2nd bank chips, or just take them one at a time.