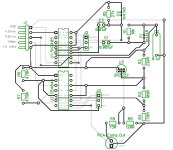

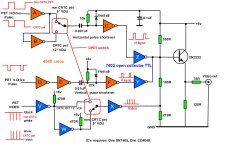

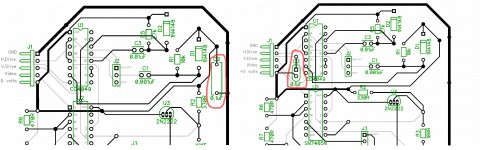

There are some mix ups on the pcb labels, briefly it shows the H & V drive inputs connecting to what is labelled as the 7405, but of course those feed the 4049. If I just swap those IC labels though, then the IC's supply pins are wrong. And of course the 4049 is a 16 pin IC, not 14 pin, + power on pin 1 and gnd on pin 8. But the diagram shows two 14 pin IC's.

Yes, it pays to check for non standard supply pins on IC's, the other common garden non standard one is the 7493.

One other thing to consider, the 4000 series cmos were super fragile to electrostatic damage. The B suffix series better. But still, the input to a cmos gate simply looks electrically like a very small value capacitor and substrate protection diodes are not all that robust.

From the relation V= Q/C, with the capacitance C so small it doesn't take much electric charge Q to raise the input voltage V very high and destroy the gate. So adding some additional diode protection on input pins can help, if you make some module, where the input pins of cmos gates just go to a connector and the module can be sitting around unplugged on a bench sometime, and you walk over to it, get charged up, and pick up the board.

On the H drive and V drive cmos gate inputs, a 1N4148 diode to the + and - supply rails protects them well. Cathode of upper diode to +5V and anode of lower diode to ground. The diodes don't conduct in normal use, but will if the unit is unplugged and a bolus of charge comes along. One other option which helps a little if there are floating cmos inputs at times, on modules etc, is to use a tie resistor to ground of a high value to ground or+5 that won't interfere with any circuit driving the input, like 47k to 100k, or in this case it could be lower added as 4.7k to 10k pull up resistor to +5v, because the inputs are driven by TTL out of the PET (I think has pullups in the VDU). At least the resistor depletes any gate charge in the condition when the module is not plugged in.

So probably the simple thing is just add 4.7k or 10k pullup resistors to +5v on the inputs of the two 4049 gates fed by the H & V drive signals. I probably should have thought to put those two extra resistors on the diagram, because it also makes the cmos input more compatible with TTL outputs, in cases where there no existing pull-ups on the TTL output.

On the other hand, floating TTL inputs are relatively robust and can be left like that on some module that gets unplugged from time to time.

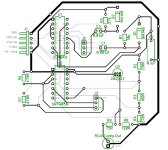

Also, on an actual pcb it pays to make all the ground tracks as wide as possible, don't scrimp on the copper in the ground tracks, but the more you leave the less is etched away.

There are lots of manufacturer variants of the 4049:

HEF4049 (Phillips), MC14049 (Motorola), CD4049 (Texas Instruments and National & RCA) etc. And they are available in plastic & ceramic packages.