RetroGadgetMan

Experienced Member

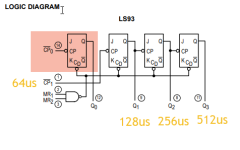

I agree. Usually my approach due to lack of knowledge would be to go around replacing parts until I reach the culprit. This has been alot more time consuming but I have learnt alot and enjoyed it. The flip flops and frequencies confuse me though.But it is a very cool circuit. I like the fact we can get inside it.

If one of many failures occurs inside a CRTC chip, it spoils fault finding fun, because you put in a new one and the fault goes away and you are none the wiser what the fault was, almost too easy and not as much fun.

I kind of prefer circuits with lots of TTL IC's rather than LSI chips for this reason. Plus, nearly all the original TTL's are still easy to get, unlike a lot of more modern parts that go obsolete ASAP. I'm glad my PET has this interesting & unusual circuit and not the CRTC chip !

Plus, the more faults that crop up in it as time goes by and we problem solve them, the more familiar we will become with the circuit. You don't get that learning experience, not to the same extent at least, plugging in new LSI chips.

Last edited: